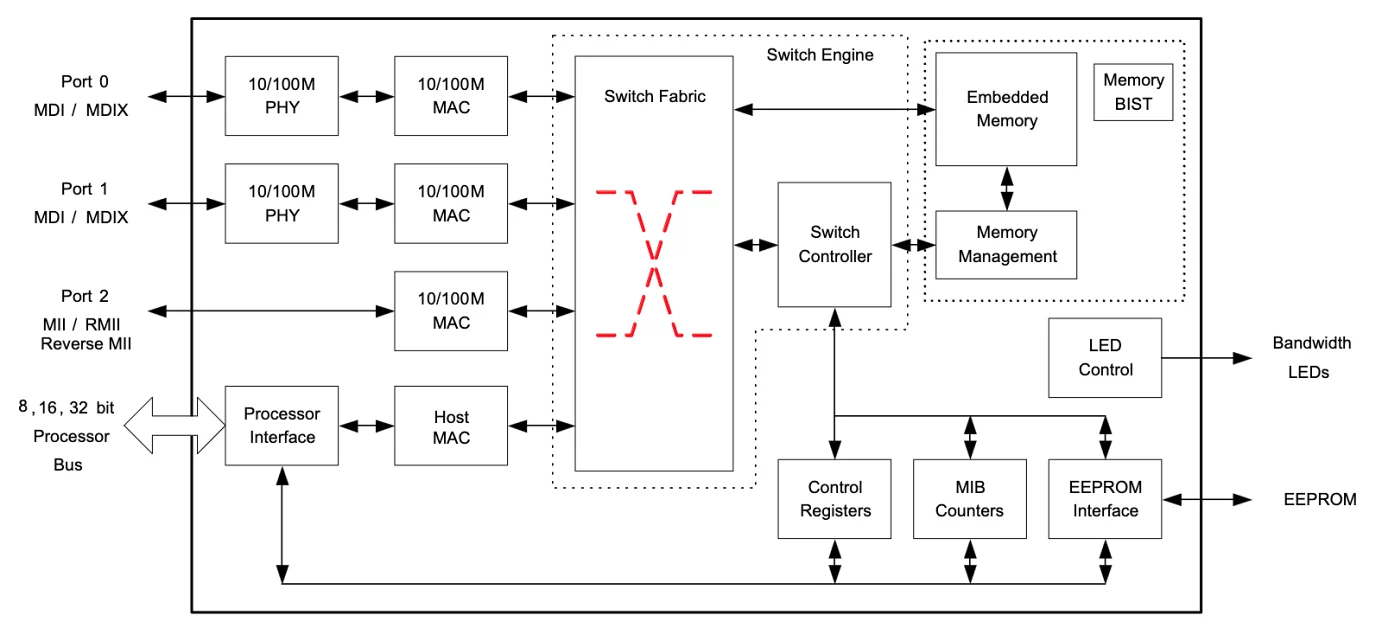

DM9016 10/100 Mbps 3-port Ethernet Switch Controller with General Processor Interface

The DM9016 is a fully integrated and cost-effective fast Ethernet switch controller with two ports 10M/100M PHY, one port MII or RMII or Reverse MII interface, and general processor bus interface. The integrated two ports PHY are compliant with IEEE 802.3u standards and support HP Auto-MDIX capabilities for twisted-pair cable transmit/receive direction automatic switching. The MII interface provides the flexibility to connect Ethernet PHY or SoC with MII/RMII interface. The general processor bus can be configured as 8-, 16-, or 32-bit data width.

Features

- Ethernet Switch with two 10/100Mb PHY, one MII/RMII/Reverse-MII port, and a flexible 8, 16, or 32-bit general processor bus interface

- Store and Forward switching approach

- Support HP Auto-MDIX

- Support up-to 1K Unicast MAC addresses

- Support IEEE 802.3x Flow Control in Full-duplex mode

- Support Back Pressure Flow Control in Half-duplex mode

- Per port supports ingress or egress bandwidth rate control

- Support Broadcast/Multicast Storm Suppression

- Support maximum packet length up to 1536(default)/1800/2032 bytes

- Support head of Line (HOL) blocking prevention

- Support MIB counters for diagnostic

- General processor bus is slave architecture

- General processor bus driving capability is adjustable

- General processor bus supports TCP/UDP/IPv4 checksum offload

- EEPROM interface for power up configuration

- Support EEPROM 93C46/93C56 with auto-detecting

- Driving capability of TXD/TXE of MII is adjustable

- Per port supports 4 level priority queues by Port-based, 802.1p VLAN, and IP TOS priority. The priority queue can be set at WRR(Weighted Round Robin) or Strictly(High priority queue first)

- Support 802.1Q VLAN up-to 16 VLAN group.

- Support VLAN ID tag/untag options

- MAC Address Table is accessible

- Support 256-entry multicast address table

- Support port security function

- Support 32 entry hardware-based IGMP Snooping V1, V2

- Support IPv6 Multicast Listener Discovery (MLD) Snooping V1

- Support Spanning Tree Protocol

- 128 QFP package with 0.18um technology

- 1.8V internal core, 3.3V I/O with 5V tolerant

Each port of the DM9106 provides four priority transmit queues, that can be defined by port-based, 802.1p VLAN, or IP packet ToS field automatically, to fit the various bandwidth and latency requirement of data, voice, and video applications. Each port also supports ingress and/or egress rate control to provide proper bandwidth. And up to 16 groups of 802.1Q VLAN with Tag/Un-tag functions are supported to provide efficient packet forwarding. The TCP/UDP/IPv4 checksum generation and checking functions are also provided by PCI port to offload the processor computing loading. Besides the packet transmit and receive functions, the PCI port also provides various registers to control and get status of the DM9106 functional operation. Each port, including the PCI port, provides the MIB counters and loop-back capability and the build in memory self test (BIST) for system and board level diagnostic. The integrated two ports PHY are compliant with IEEE 802.3u standards. The MII interface provides the flexibility to connect Ethernet PHY, and it can be configured as Reversed MII interface for SoC with MII interface. An alternative interface, the RMII interface, is also provided to connect the lower pin count Ethernet PHY or SoC with RMII interface.