DM9051(I) SPI to Ethernet Controller

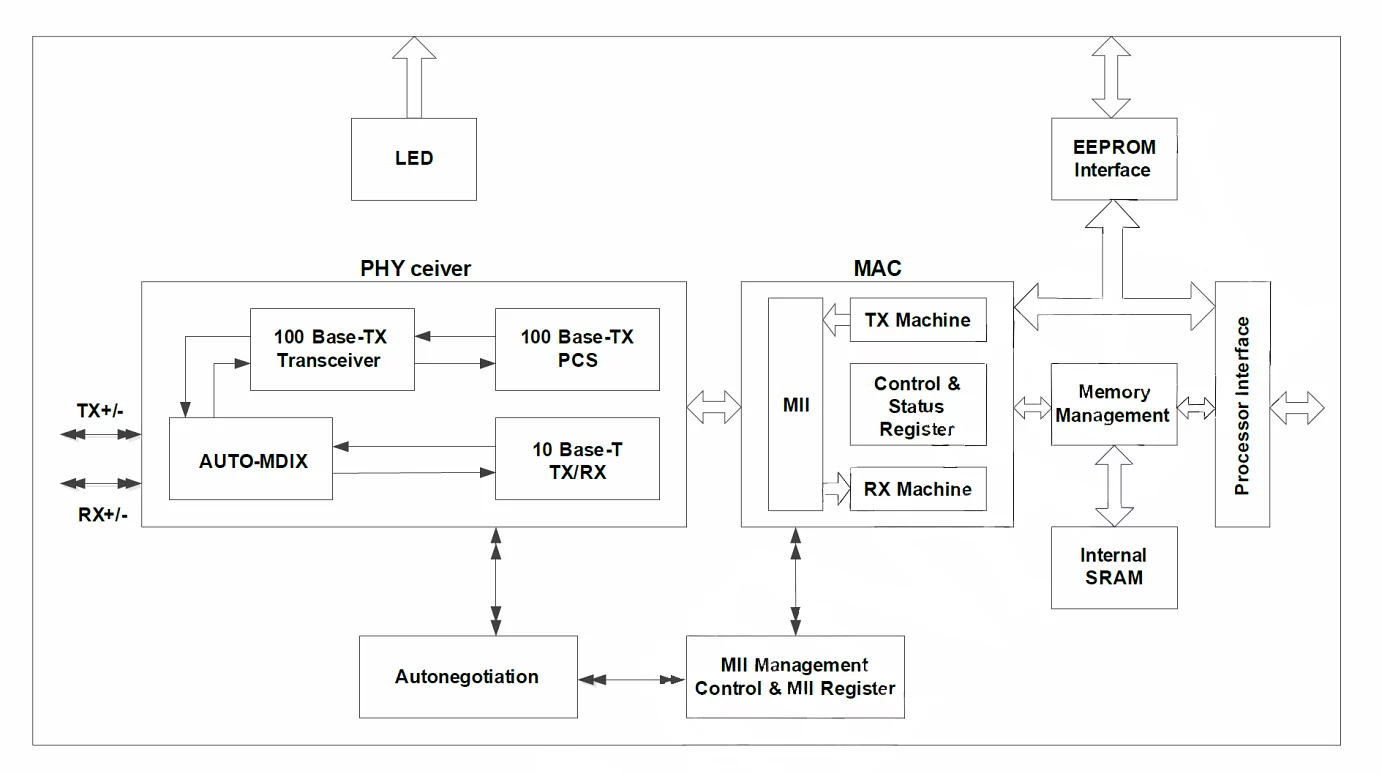

The DM9051(I) is a fully integrated and cost-effective low pin count single chip Fast Ethernet controller with a Serial Peripheral Interface (SPI), a 10/100M PHY and MAC, and 16K-byte SRAM. It is designed with low power and high performance process interface that support 3.3V with 5V IO tolerance. The PHY of the DM9051(I) can interface to the UTP3, 4, 5 in 10Base-T and UTP5 in 100Base-TX with HP Auto-MDIX.It is fully compliant with the IEEE 802.3u Spec. Its Auto-Negotiation function will automatically configure the DM9051(I) to take the maximum advantage of its 10M or 100M abilities. The DM9051(I) supports IEEE 802.3az in PHY and MAC to save power consumption when Ethernet is idle. The IEEE 802.3x Full-Duplex flow control and Half-Duplex back-pressure function also supported to avoid Ethernet packet loss with link partner.

Features

- Slave SPI Interface with clock speeds up to 50MHz for high throughput applications

- Support SPI clock mode 0 and 3

- Support 10BASE-T and 100BASE-TX and 100M Fiber interface

- Support HP Auto-MDIX crossover function in 10BASE-T and 100BASE-TX

- Support IEEE 802.3az Energy Efficient Ethernet (EEE)

- Support interface for EEPROM to configure chip settings

- Support back pressure flow control for Half-Duplex mode

- Support IEEE802.3x flow control for Full-Duplex mode

- Supports wake up frame, link status change and magic packet events to generate remote wake on LAN (WOL) signal

- Support IPv4 / TCP / UDP checksum generation and checking

- Configurable of internal transmit / receive buffers within 16K-byte memory

- Built - in integrated 3.3V to 1.8V low noise regulator for core and analog blocks

- Support EMI (Class B) and HBM ESD Rating 8KV

- Support Industrial Temperature Range: –40°C to +85°C (DM9051I)

- 3.3V I/O with 5V tolerant

- DSP architecture PHY Transceiver

- 0.18umprocess

The slave SPI interface is designed to support SPI clock mode 0 and 3 that compatible with the all master SPI interface of CPU. The clock speed can up to 50Mhz to co-operation with most high throughput master SPI. The SPI burst command format is code-effective to minimize the command overhead in access DM9051(I) internal registers and packet data in memory.