DM9051(I) SPI to Ethernet Controller

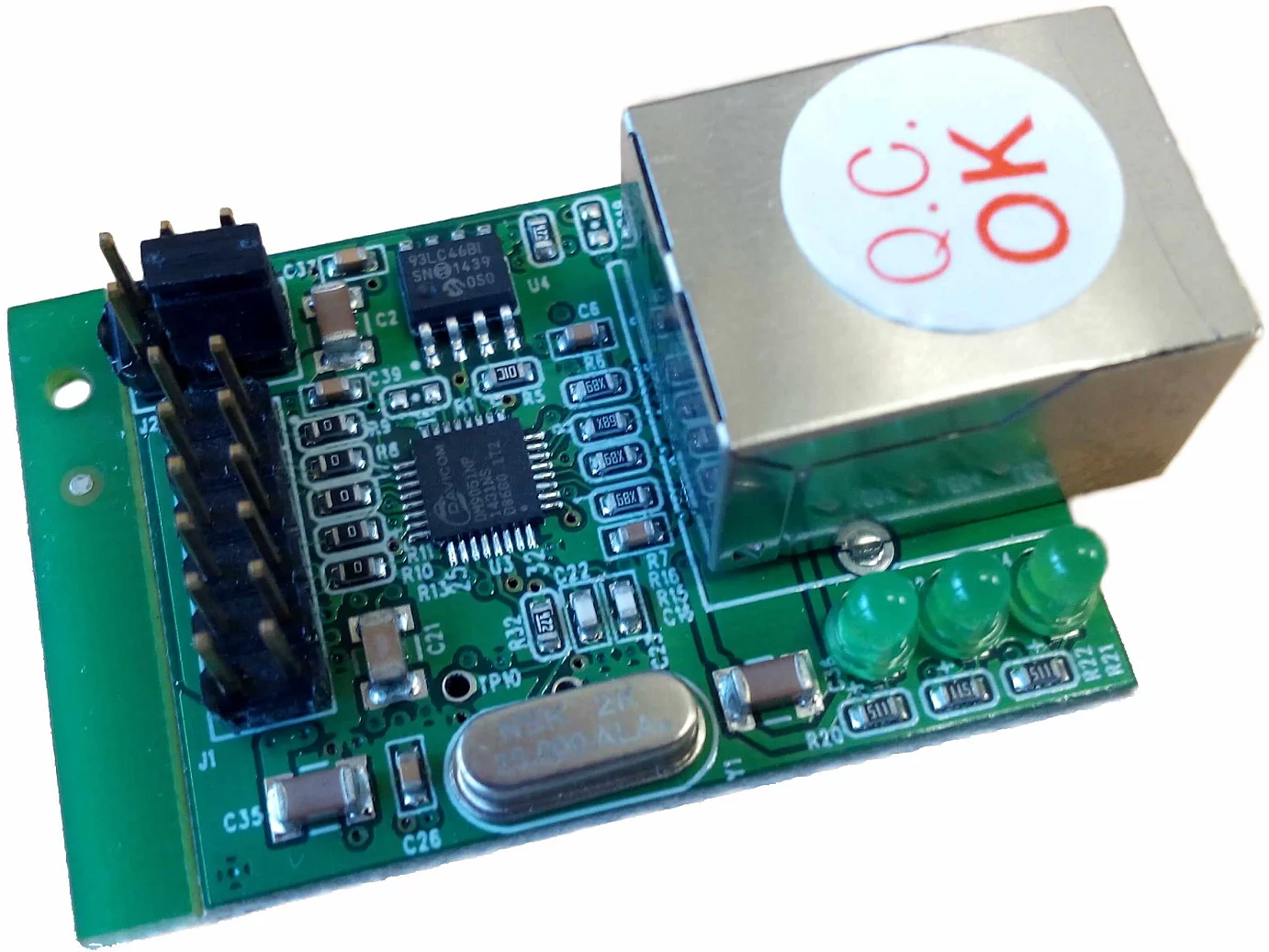

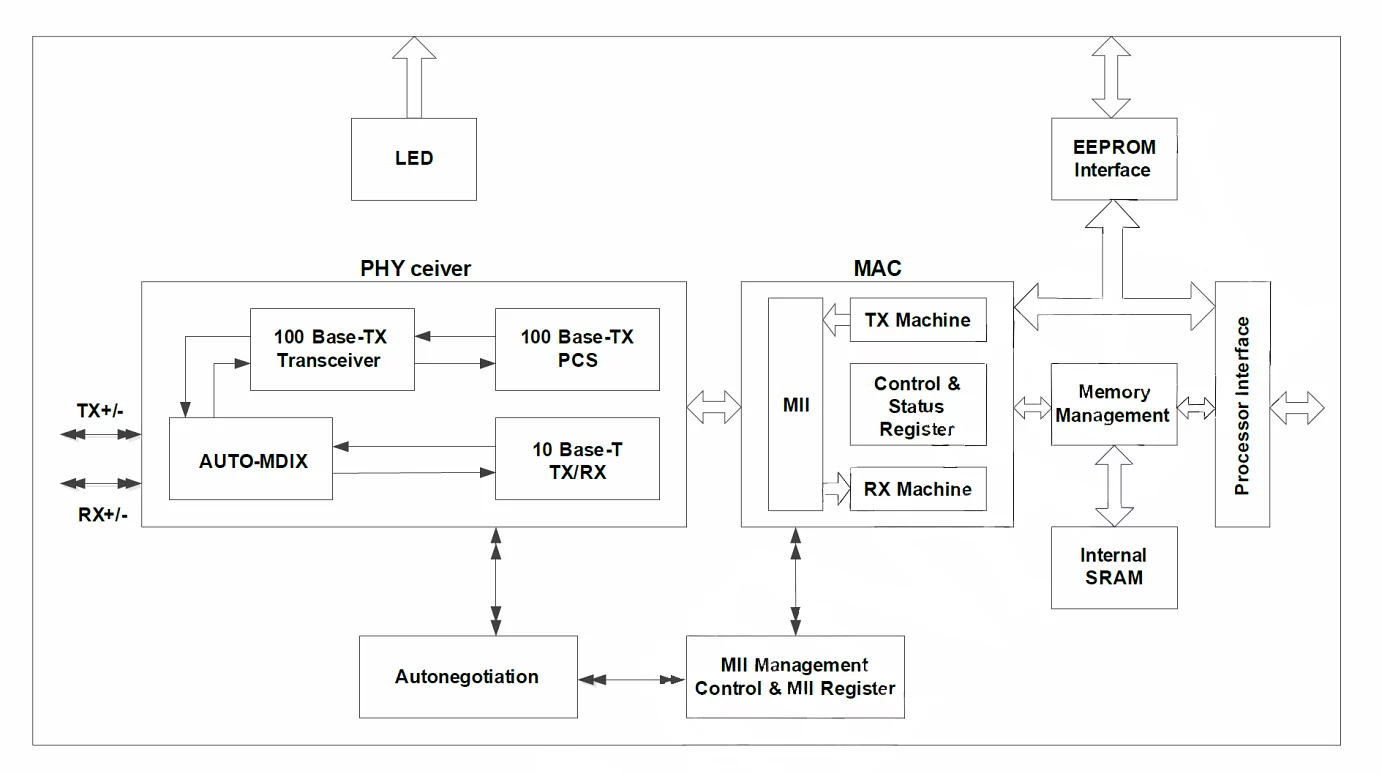

Der DM9051(I) ist ein voll integrierter und kostengünstiger Single-Chip-Fast-Ethernet-Controller mit geringer Pinzahl, serieller Peripherieschnittstelle (SPI), 10/100M PHY und MAC sowie 16K-Byte SRAM. Er wurde mit einer stromsparenden und hochleistungsfähigen Prozessschnittstelle entwickelt, die 3,3V mit 5V IO-Toleranz unterstützt. Der PHY des DM9051(I) kann eine Schnittstelle zu UTP3, 4, 5 in 10Base-T und UTP5 in 100Base-TX mit HP Auto-MDIX bilden und ist vollständig konform mit der IEEE 802.3u Spezifikation. Seine Auto-Negotiation-Funktion konfiguriert den DM9051(I) automatisch so, dass er seine 10M- oder 100M-Fähigkeiten optimal ausnutzt. Der DM9051(I) unterstützt IEEE 802.3az in PHY und MAC, um den Stromverbrauch zu senken, wenn das Ethernet im Leerlauf ist. Die IEEE 802.3x Full-Duplex-Flusskontrolle und die Half-Duplex-Back-Pressure-Funktion werden ebenfalls unterstützt, um den Verlust von Ethernet-Paketen bei Verbindungspartnern zu vermeiden.

Features

- Slave SPI Interface with clock speeds up to 50MHz for high throughput applications

- Support SPI clock mode 0 and 3

- Support 10BASE-T and 100BASE-TX and 100M Fiber interface

- Support HP Auto-MDIX crossover function in 10BASE-T and 100BASE-TX

- Support IEEE 802.3az Energy Efficient Ethernet (EEE)

- Support interface for EEPROM to configure chip settings

- Support back pressure flow control for Half-Duplex mode

- Support IEEE802.3x flow control for Full-Duplex mode

- Supports wake up frame, link status change and magic packet events to generate remote wake on LAN (WOL) signal

- Support IPv4 / TCP / UDP checksum generation and checking

- Configurable of internal transmit / receive buffers within 16K-byte memory

- Built - in integrated 3.3V to 1.8V low noise regulator for core and analog blocks

- Support EMI (Class B) and HBM ESD Rating 8KV

- Support Industrial Temperature Range: –40°C to +85°C (DM9051I)

- 3.3V I/O with 5V tolerant

- DSP architecture PHY Transceiver

- 0.18umprocess

Die Slave-SPI-Schnittstelle ist so konzipiert, dass sie die SPI-Taktmodi 0 und 3 unterstützt, die mit der Master-SPI-Schnittstelle der CPU kompatibel sind. Die Taktgeschwindigkeit kann bis zu 50Mhz betragen, um mit den meisten Master-SPIs mit hohem Durchsatz zusammenzuarbeiten. Das SPI-Burst-Befehlsformat ist code-effektiv, um den Befehls-Overhead beim Zugriff auf interne DM9051(I)-Register und Paketdaten im Speicher zu minimieren.

Features

- Slave SPI Interface with clock speeds up to 50MHz for high throughput applications

- Support SPI clock mode 0 and 3

- Support 10BASE-T and 100BASE-TX and 100M Fiber interface

- Support HP Auto-MDIX crossover function in 10BASE-T and 100BASE-TX

- Support IEEE 802.3az Energy Efficient Ethernet (EEE)

- Support interface for EEPROM to configure chip settings

- Support back pressure flow control for Half-Duplex mode

- Support IEEE802.3x flow control for Full-Duplex mode

- Supports wake up frame, link status change and magic packet events to generate remote wake on LAN (WOL) signal

- Support IPv4 / TCP / UDP checksum generation and checking

- Configurable of internal transmit / receive buffers within 16K-byte memory

- Built - in integrated 3.3V to 1.8V low noise regulator for core and analog blocks

- Support EMI (Class B) and HBM ESD Rating 8KV

- Support Industrial Temperature Range: –40°C to +85°C (DM9051I)

- 3.3V I/O with 5V tolerant

- DSP architecture PHY Transceiver

- 0.18umprocess

Die Slave-SPI-Schnittstelle ist so konzipiert, dass sie die SPI-Taktmodi 0 und 3 unterstützt, die mit der Master-SPI-Schnittstelle der CPU kompatibel sind. Die Taktgeschwindigkeit kann bis zu 50Mhz betragen, um mit den meisten Master-SPIs mit hohem Durchsatz zusammenzuarbeiten. Das SPI-Burst-Befehlsformat ist code-effektiv, um den Befehls-Overhead beim Zugriff auf interne DM9051(I)-Register und Paketdaten im Speicher zu minimieren.