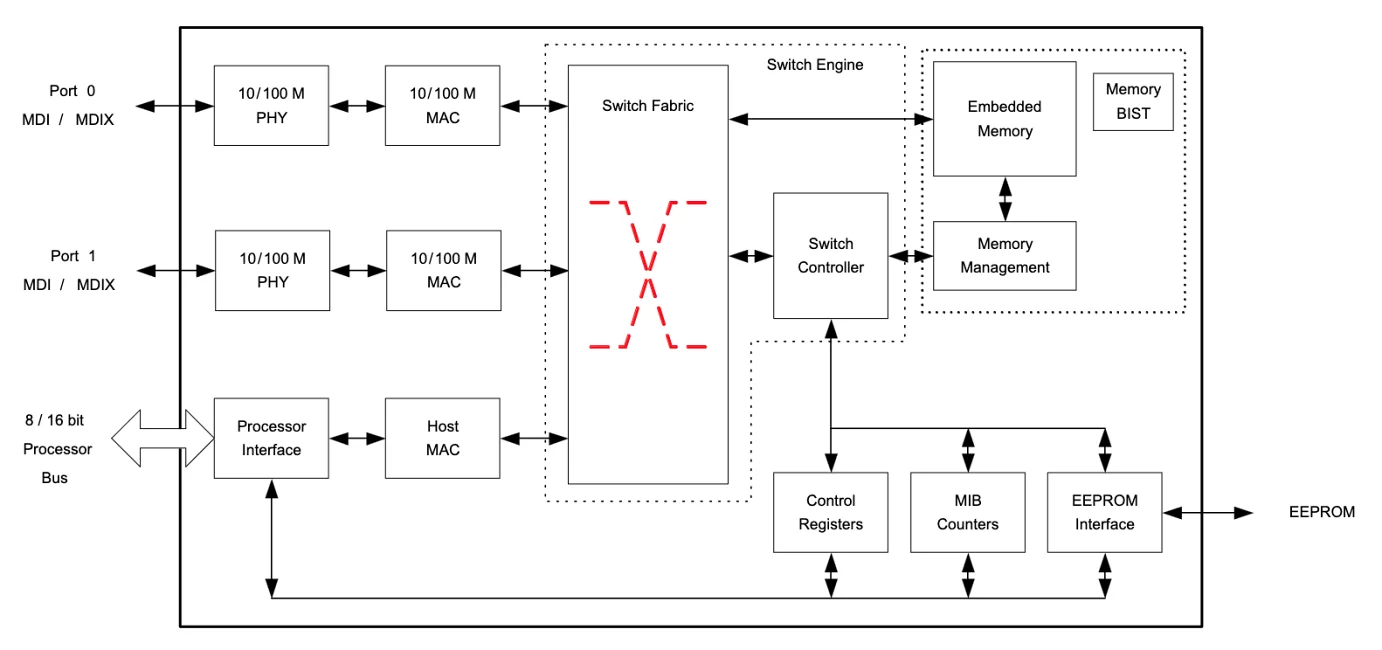

DM9006 10/100 Mbps 2-Port Ethernet Switch Controller mit allgemeiner Prozessorschnittstelle

Der DM9006 ist ein vollständig integrierter und kostengünstiger Fast-Ethernet-Switch-Controller mit zwei 10M/100M-PHY-Ports und allgemeiner Prozessorbus-Schnittstelle. Der integrierte PHY mit zwei Anschlüssen entspricht den IEEE 802.3u-Standards und unterstützt HP Auto-MDIX-Funktionen für die automatische Umschaltung der Sende-/Empfangsrichtung von Twisted-Pair-Kabeln. Der allgemeine Prozessorbus kann als 8-Bit- oder 16-Bit-Datenbreite konfiguriert werden. Der DM9006 ist ein gemanagter Switch und bietet nicht nur

Er bietet nicht nur grundlegende Layer-2-Switch-Funktionen, sondern auch erweiterte Funktionen wie 802.1Q VLAN, Prioritäts-Warteschlangenverwaltung, Bandbreitensteuerung, Überwachung des Port-Verkehrs, Filterung von Multicast-Paketen, Port-Sicherheit und hardwarebasiertes IGMP V1/V2 Snooping usw.

DM9006 Block diagram

Features

- Ethernet-Switch mit zwei 10/100Mb PHY und einer flexiblen 8-Bit- oder 16-Bit-General-Prozessor-Bus-Schnittstelle

- Store and Forward Switching-Ansatz

- Unterstützung von HP Auto-MDIX

- Unterstützung von bis zu 1K Unicast MAC-Adressen

- Unterstützung von IEEE 802.3x Flow Control im Vollduplex-Modus

- Unterstützung von Back Pressure Flow Control im Halbduplex-Modus

- Unterstützt pro Port die Bandbreitenkontrolle am Eingang oder Ausgang

- Unterstützt Broadcast/Multicast Storm Suppression

- Unterstützt eine maximale Paketlänge von bis zu 1536 (Standard)/2032 Bytes

- Unterstützt Head of Line (HOL) Blocking Prevention

- Unterstützung von MIB-Zählern für die Diagnose

- Allgemeiner Prozessorbus ist Slave-Architektur

- Die Treiberfähigkeit des allgemeinen Prozessorbusses ist einstellbar

- Allgemeiner Prozessorbus unterstützt TCP/UDP/IPv4-Prüfsummen-Offload

- EEPROM-Schnittstelle für die Konfiguration beim Einschalten

- Unterstützt EEPROM 93C46/93C56 mit automatischer Erkennung

- Ansteuerungsfähigkeit von TXD/TXE von MII ist einstellbar

- Jeder Port unterstützt 4 Prioritäts-Warteschlangen mit Port-basierter, 802.1p VLAN- und IP TOS-Priorität. Die Prioritätswarteschlange kann auf WRR (Weighted Round Robin) oder Strictly (High priority queue first) eingestellt werden.

- Unterstützt 802.1Q VLAN bis zu 16 VLAN-Gruppen.

- Unterstützt VLAN ID tag/untag Optionen

- MAC-Adresstabelle ist zugänglich

- Unterstützt Multicast-Adresstabelle mit 256 Einträgen

- Unterstützung der Port-Sicherheitsfunktion

- Unterstützt 32 Einträge hardwarebasiertes IGMP Snooping V1, V2

- uP-Datentreiberfähigkeit einstellbar

- 64-Pin LQFP 1.8V interner Kern, 3.3V I/O mit 5V Toleranz

- Unterstützung von bleifreien und halogenfreien Materialien

Der allgemeine Prozessorbus kann als 8-, 16- oder 32-Bit-Datenbreite konfiguriert werden und bietet Schnittstellen zu den meisten Embedded-CPUs. Das DM9006 bietet eine TCP/UDP/IPv4-Prüfsummen-Offload-Funktion, um die Host-CPU zu entlasten und die Systemleistung zu verbessern. Der einstellbare Sende-/Empfangspuffer des Prozessorports kann die CPU bei der Verarbeitung von Anwendungen wie Video- und Voice-Streaming entlasten. Für die Energieverwaltung unterstützt das DM9006 die Wake-on-LAN-Funktion über die Änderung des Verbindungsstatus oder die Erkennung magischer Pakete. Darüber hinaus sind die MIB-Zähler, die Loop-Back-Fähigkeit und der Speicher-Build-in-Selbsttest (BIST) nützlich für die Diagnose auf System- und Kartenebene.